ایستگاه بازسازی خودکار نوری BGA

به طور گسترده ای در تعمیرات سطح تراشه برای مادربردهای موبایل، لپ تاپ، کامپیوتر، تلویزیون، تهویه مطبوع و غیره استفاده می شود. دارای نرخ موفقیت آمیز بالای تعمیر و درجه بالایی از اتوماسیون است و باعث صرفه جویی در بسیاری از تلاش های انسان می شود. ما تولید کننده حرفه ای این دستگاه هستیم و این دستگاه ها را در انبار داریم.

شرح

ایستگاه بازسازی خودکار نوری BGA

1.Application Auto Optical BGA Rework Station

مادربرد کامپیوتر، تلفن هوشمند، لپ تاپ، برد منطقی مک بوک، دوربین دیجیتال، تهویه مطبوع، تلویزیون و سایر الکترونیک

تجهیزات صنعت پزشکی، صنعت ارتباطات، صنعت خودرو و غیره

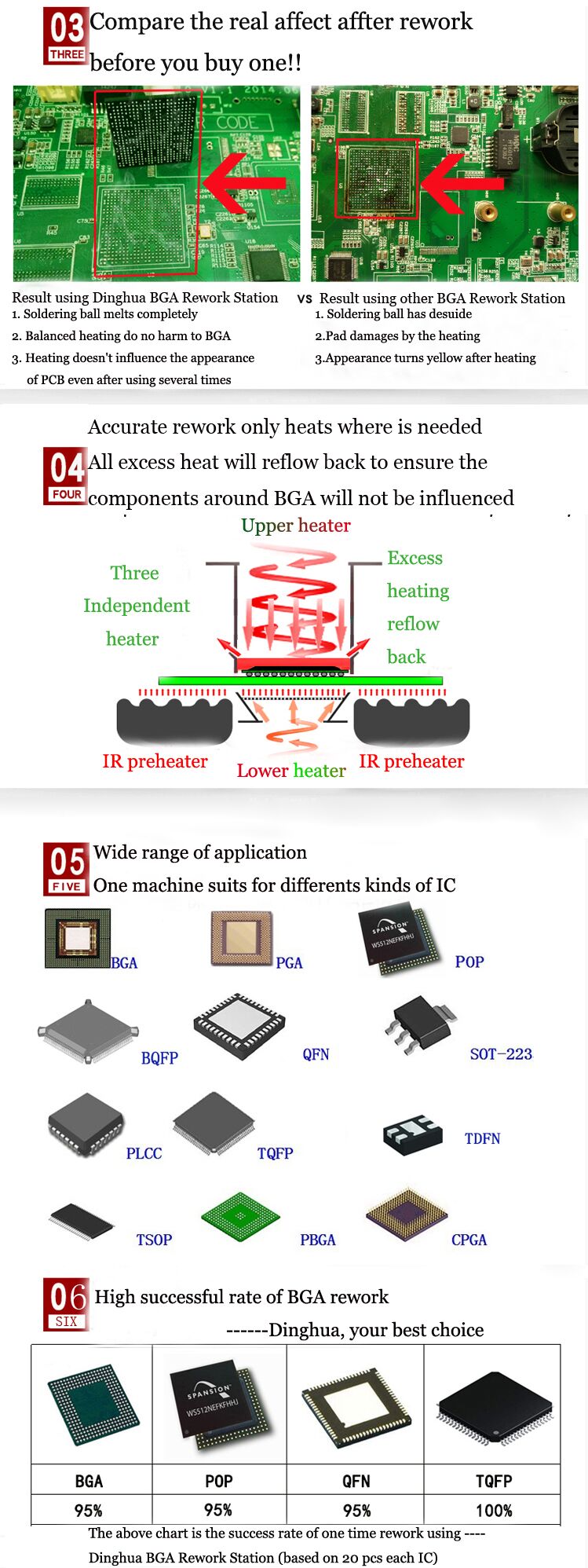

مناسب برای انواع مختلف تراشه: BGA، PGA، POP، BQFP، QFN، SOT223، PLCC، TQFP، TDFN، TSOP، PBGA، CPGA، تراشه LED.

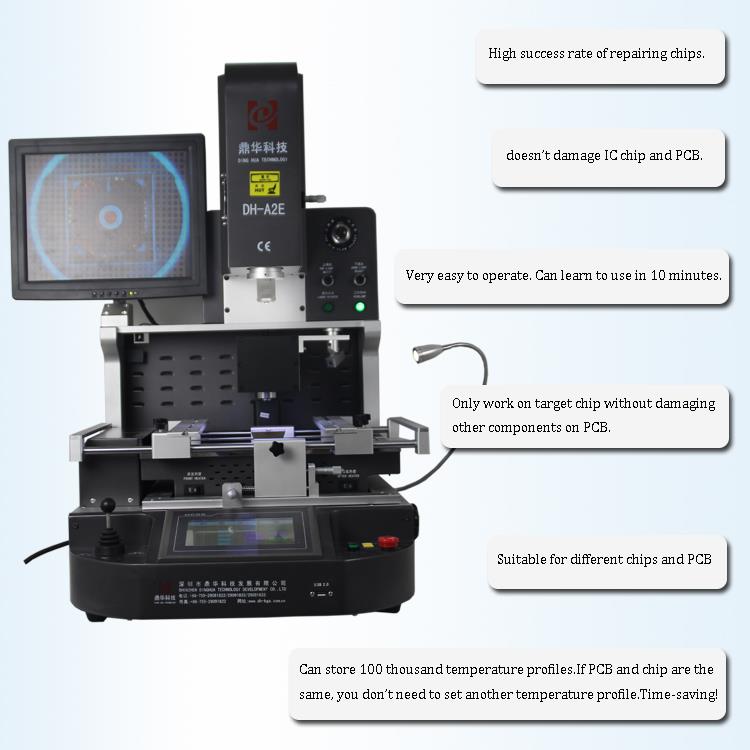

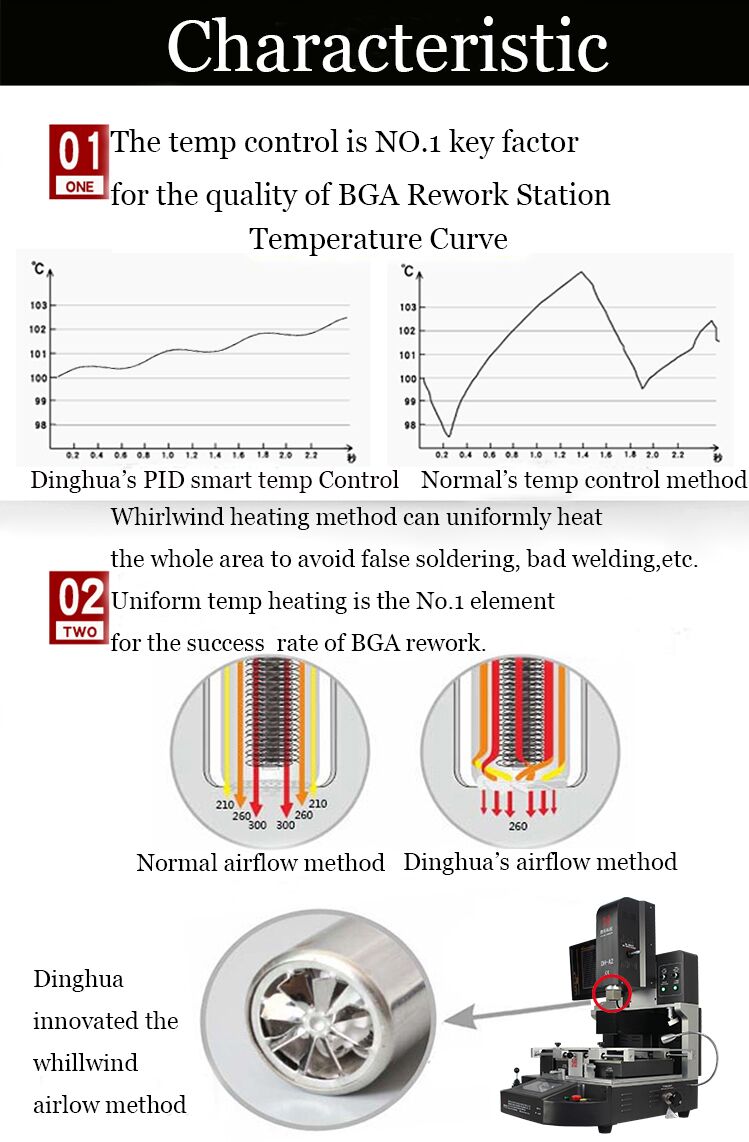

2.ویژگی های محصول ایستگاه مجدد کار نوری خودکار BGA

• میزان موفقیت بالای تعمیر در سطح تراشه. فرآیند لحیم کاری، نصب و لحیم کاری خودکار است.

• تراز دقیق هر مفصل لحیم کاری را می توان با دوربین CCD تنظیم نوری تضمین کرد.

•کنترل دما دقیق را می توان با 3 ناحیه گرمایش مستقل تضمین کرد. دستگاه می تواند تنظیم و ذخیره کند

1 میلیون مشخصات دما

• جاروبرقی تعبیه شده در سر نصب، تراشه BGA را به طور خودکار پس از اتمام لحیم کاری جمع آوری می کند.

3. مشخصات خودکار نوری BGA ایستگاه مجدد

4.جزئیات خودکار نوری BGA ایستگاه مجدد

دوربین CCD (سیستم تراز نوری دقیق)؛ صفحه نمایش دیجیتال 2.HD; 3. میکرومتر (تنظیم زاویه تراشه)؛

4.3 بخاری مستقل (هوای گرم و مادون قرمز)؛ 5. تعیین موقعیت لیزری. 6. رابط صفحه نمایش لمسی HD، کنترل PLC.

7. چراغ جلو ; 8. کنترل جوی استیک.

5. چرا ایستگاه بازکاری نوری خودکار BGA را انتخاب کنید؟

6. گواهی خودکار نوری BGA ایستگاه مجدد

7. بسته بندی و حمل و نقل خودکار نوری BGA ایستگاه مجدد

8. سوالات متداول

چگونه تراشه را تست کنیم؟

آزمایش اولیه تراشه در سطح سیستم

SoC مبتنی بر فرآیندهای زیر میکرون عمیق است، بنابراین آزمایش دستگاه های جدید Soc نیازمند یک رویکرد کاملاً جدید است. زیرا هر جزء کاربردی

دارای الزامات آزمایشی خاص خود است، مهندس طراح باید در مراحل اولیه طراحی یک برنامه آزمایشی تهیه کند.

طرح آزمایش بلوک به بلوک برای دستگاههای SoC باید اجرا شود: ابزارهای ATPG با پیکربندی مناسب برای تست منطقی. زمان آزمون کوتاه؛ پرسرعت جدید

مدل های خطا و چندین حافظه یا آزمایش های آرایه کوچک. برای خط تولید، روش تشخیصی نه تنها عیب را پیدا می کند، بلکه آن را جدا می کند

گره معیوب از گره کار. بعلاوه، برای صرفه جویی در زمان تست، باید در صورت امکان از تکنیک های مالتی پلکس تست استفاده شود. در زمینه بسیار

تست IC یکپارچه، تکنیک های طراحی قابل آزمایش ATPG و IDDQ دارای مکانیزم جداسازی عیب قدرتمندی هستند.

سایر پارامترهای واقعی که باید از قبل برنامه ریزی شوند عبارتند از تعداد پین هایی که باید اسکن شوند و مقدار حافظه در انتهای هر پین.

اسکنهای مرزی را میتوان روی SoC تعبیه کرد، اما به آزمایشهای اتصال روی بردها یا ماژولهای چند تراشه محدود نمیشود.

اگرچه اندازه تراشه در حال کاهش است، یک تراشه هنوز هم می تواند میلیون ها تا 100 میلیون ترانزیستور را بسته بندی کند، و تعداد حالت های تست به بی سابقه ای افزایش یافته است.

سطوح، که منجر به چرخه های آزمایش طولانی تر می شود. این مشکل قابل آزمایش است. حالت فشرده سازی برای حل، نسبت فشرده سازی می تواند به 20 درصد تا 60 درصد برسد. برای مقیاس بزرگ امروزی

طراحی تراشه، برای جلوگیری از مشکلات ظرفیت، لازم است نرم افزار آزمایشی را پیدا کنید که بتواند روی سیستم عامل های 64-بیتی اجرا شود.

علاوه بر این، نرم افزار تست با مشکلات جدید تست ناشی از فرآیندهای زیر میکرون عمیق و افزایش فرکانس مواجه است. در گذشته، حالت تست ATPG برای

آزمایش خطاهای مسدود کننده استاتیک دیگر قابل اجرا نبود. افزودن الگوهای کاربردی به ابزارهای سنتی، یافتن خطاهای جدید را دشوار می کرد. رویکرد بهتر این است که

گروههای حالت عملکردی گذشته را طبقهبندی کنید تا مشخص کنید کدام خطاها قابل شناسایی نیستند، و سپس یک حالت ATPG ایجاد کنید تا این انواع خطاهای گمشده را ثبت کنید.

با افزایش ظرفیت طراحی و کاهش زمان تست هر ترانزیستور، به منظور یافتن مشکلات مربوط به سرعت و تأیید زمان بندی مدار، یک روش تست همزمان

باید به کار گرفته شود. تست همزمان باید چندین مدل خطا از جمله مدلهای گذرا، تاخیرهای مسیر و IDDQ را در خود جای دهد.

برخی از شرکتهای صنعت بر این باورند که ترکیب خطاهای مسدود کردن، عملکردی و تاخیر گذرا/مسیر ممکن است موثرترین استراتژی تست باشد. برای عمیق

تراشه های زیر میکرون و عملکرد فرکانس بالا، آزمایش گذرا و تاخیر مسیر حتی مهم تر است.

برای حل مشکل دقت ATE هنگام همگام سازی هسته تست و کاهش هزینه، لازم است روش جدیدی پیدا شود که رابط کاربری را ساده کند.

دستگاه تست (تست گذرا و تاخیر مسیر به ساعت دقیق در رابط دستگاه تست نیاز دارد)، این اطمینان را می دهد که سیگنال در طول آزمایش به اندازه کافی دقیق است.

از آنجایی که احتمال ایجاد نقص در بلوک حافظه SoC زیاد است، حافظه BIST باید یک عملکرد تشخیصی داشته باشد. وقتی مشکلی پیدا شد،

واحد آدرس معیوب را می توان به حافظه اضافی واحد آدرس یدکی نگاشت کرد و آدرس خطای شناسایی شده حذف خواهد شد. از دور انداختن خودداری کنید

کل تراشه گران قیمت

آزمایش بلوک های حافظه جاسازی شده کوچک، نیاز به گیت های اضافی یا منطق کنترل را از بین می برد. به عنوان مثال، تکنیک های تست تبدیل برداری می توانند تبدیل شوند

حالت های کاربردی را به یک سری حالت اسکن تبدیل کنید.

برخلاف روش BIST، ورودی عملکردی بلوک حافظه بای پس نیازی به منطق اضافی ندارد. از آنجا که هیچ منطق تست اضافی مورد نیاز نیست، SoC

مهندسان توسعه میتوانند از الگوهای آزمایشی که در گذشته شکل گرفتهاند دوباره استفاده کنند.

ابزارهای پیشرفته ATPG نه تنها ماکروها را به صورت موازی آزمایش میکنند، بلکه تعیین میکنند که آیا تداخل وجود دارد یا خیر، و همچنین توضیح میدهد که کدام ماکروها را میتوان به صورت موازی آزمایش کرد و کدام یک

ماکروها را نمی توان به صورت موازی آزمایش کرد. علاوه بر این، حتی اگر ساعت ماکرو با ساعت اسکن (مانند حافظه سنکرون) یکسان باشد، این ماکروها را می توان به طور موثر آزمایش کرد.

در حال حاضر نقاط تست کافی روی برد دو طرفه متراکم وجود ندارد و هر تراشه پیچیده باید به مدار اسکن مرزی مجهز باشد. بدون

اسکن مرز، جستجوی نقص تولید در سطح برد بسیار دشوار است و حتی نمی توان آن را پیدا کرد. با اسکن مرزی، آزمایش در سطح برد بسیار آسان است

و مستقل از مدار منطقی درون تراشه. اسکن مرزی همچنین می تواند حالت ATPG را برای زنجیره اسکن تراشه در هر مرحله از تولید پیکربندی کند.